Главная страница / 7. Основные этапы развития вычислительно...: 7.3. Принцип работы вычис...

7.3. Принцип работы вычислительной системы

| ← 7.2. Архитектура ЭВМ | 7.4. Контрольные вопросы и задания → |

В этой главе рассматривается принцип действия цифровых устройств, процессора, приведена историческая справка, относящаяся к хронологии развития процессоров, описан принцип работы арифметико-логического устройства, оперативной памяти, внешних запоминающих устройств, устройств ввода информации в ЭВМ и устройств вывода информации.

Основными элементами современных ЭВМ являются цифровые устройства. Это объясняется тем, что при разработке новых конструкций компьютеров проверялись на практике различные варианты их построения. Изобретались вычислительные средства, в которых сигналы могли изменяться непрерывно (аналоговые ЭВМ). Были созданы конструкции, в которых основные элементы компьютера могли находиться в трех различных устойчивых состояниях (в отечественной ЭВМ «Сетунь» использовалась троичная система счисления). Существуют элементы, которые могут принимать только два устойчивых состояния (например, реле). Их контакты могут быть либо замкнуты, либо разомкнуты. Первые вычислительные машины были сконструированы с использованием реле. Работу таких элементов удобно описывать с помощью двоичной системы счисления и алгебры логики.

Радиоэлектронные элементы, которые могут принимать только два устойчивых состояния, являются цифровыми устройствами (ЦУ). Два устойчивых состояния удобно обозначать такими терминами: включено–выключено, открыто–закрыто, да–нет, истина– ложь или единица–ноль.

Достоинство цифровых устройств – их высокая помехоустойчивость и стабильность. Такие элементы надёжно работают при случайном изменении напряжения питания, окружающей температуры, при действии электромагнитных помех.

Сигналы, представленные в цифровой форме, можно копировать, передавать и хранить практически без искажений. В то же время аналоговые сигналы таковы, что их копии всегда отличаются от оригинала (искажаются).

Все цифровые устройства делятся на два класса: комбинационные ЦУ и последовательностные ЦУ (или цифровые автоматы).

В комбинационных цифровых устройствах выходной сигнал в каждый момент времени зависит только от сочетания (комбинации) входных сигналов. К таким ЦУ относятся: шифраторы, дешифраторы, мультиплексоры, демультиплексоры, преобразователи кодов, сумматоры, арифметико-логические устройства, логические элементы (И, ИЛИ, И-НЕ, ИЛИ-НЕ, Исключающее ИЛИ и др.).

Состояние последовательностных ЦУ зависит не только от входных сигналов, имеющихся в данный момент времени, но и от предшествующего состояния ЦУ. Эти элементы обладают памятью. К последовательностным цифровым устройствам относятся триггеры, счетчики, регистры.

Аппаратно-цифровые устройства могут быть реализованы на различных элементных базах: электромагнитных реле, электровакуумных ламп, дискретных транзисторов, в виде микросхем, выполненных по интегральной полупроводниковой технологии.

При работе цифровых устройств их элементы в какой-то момент времени проводят электрический ток (открытое состояние), а в другой момент времени не проводят (закрытое состояние). Таким образом, формируются сигналы логической единицы и логического нуля (цифровые сигналы).

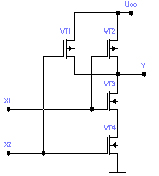

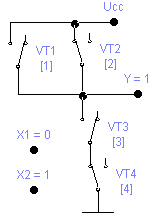

Принцип действия логических элементов рассмотрим на примере работы устройства, выполняющего логическую операцию И-НЕ (рис. 7.3).

Рис. 7.3. Схема устройства, выполняющего логическую функцию И-НЕ

Заметим, что схемотехническое построение элемента может быть различным: с использованием технологий РТЛ, РЕТЛ, ДТЛ, ТТЛ, ЭСЛ, КМОП, И2Л. Эти технологии позволяют получить элементы, отличающиеся друг от друга быстродействием, нагрузочной способностью и потребляемой мощностью (экономичностью).

Рассматриваемый элемент построен на комплементарных металл-окисел полупроводниках (полевых транзисторах, выполненных по КМОП-технологии). Термин «комплементарные» означает, что используемые транзисторы взаимно дополняют друг друга. В этих конструкциях применяются транзисторы двух типов. Транзисторы одного типа открываются высоким, а запираются низким напряжением (VT3, VT4). А другие транзисторы наоборот: запираются высоким напряжением, а низким напряжением открываются (VT1, VT2). Такие полупроводниковые элементы носят специальное название – полевые транзисторы с p-каналом и n-каналом.

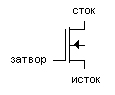

На рис. 7.4. показан полевой транзистор с изолированным затвором и каналом n-типа. Внутренняя часть транзистора между истоком и стоком называется каналом. Транзисторы работают в так называемом ключевом режиме. При этом каждый транзистор либо полностью открыт и проводит электрический ток, либо закрыт и практически ток не проводит. Переключение транзисторов из одного предельного состояния в другое происходит достаточно быстро.

Рис. 7.4. Полевой транзистор с изолированным затвором и каналом n-типа

Если попытаться изложить принцип работы транзистора с помощью метафоры, то транзистор можно сравнить с водопроводным краном. Поток воды, протекающий по трубе (каналу) от истока к стоку можно перекрывать с помощью крана. Таким краном в полевом транзисторе является затвор. Управляющее напряжение на затворе позволяет либо открыть канал (пропустить воду), либо перекрыть этот поток.

Как известно, логический элемент И-НЕ работает в соответствии со следующей таблицей истинности (табл. 7.2).

Таблица 7.2. Таблица истинности

| 2 x | 1 x | y | |

| 1 |

0 |

0 |

1 |

| 2 |

0 |

1 |

1 |

| 3 |

1 |

0 |

1 |

| 4 |

1 |

1 |

0 |

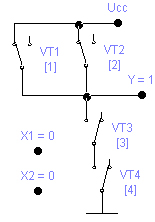

Если входные сигналы x1 и x2 равны нулю, то транзисторы VT1 и VT2 будут открыты, а транзисторы VT3 и VT4 – закрыты. Термин «открытый транзистор» означает, что сопротивление канала транзистора становится небольшим и между истоком и стоком протекает ток. Через открытые транзисторы VT3 и VT4 высокий потенциал (примерно равный напряжению питания Ucc) передается на выходной зажим Y. Высокое выходное напряжение условно обозначено логической единицей (см. верхнюю строку табл. 7.2).

Если входные сигналы x1 и x2 одновременно равны высоким потенциалам (единицам), то транзисторы VT1 и VT2 будут закрыты, а транзисторы VT3 и VT4 – открыты. В результате этого через открытые транзисторы VT3 и VT4 на выходную шину Y будет подан потенциал, близкий к нулю вольт (см. нижнюю строку табл. 7.2).

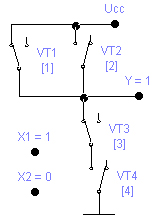

Если на входы элемента И-НЕ подать сигналы x1 = 1 и x2 = 0, то транзисторы VT3 и VT1 будут открыты, а транзисторы VT2 и VT4 закрыты. Через открытый транзистор VT1 от источника питания Ucc на выходной зажим Y поступит высокий потенциал, который соответствует логической единице.

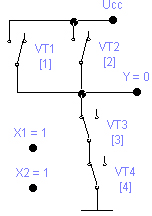

На рис. 7.5 схематично проиллюстрирована работа устройства при четырёх возможных комбинациях входных сигналов. При этом открытые транзисторы изображаются в виде замкнутых контактов переключателей, а закрытые транзисторы – в виде разомкнутых контактов.

|

|

|

|

Рис. 7.5. Четыре возможных комбинации входных сигналов

Управляющие сигналы x1 и x2 подаются на затворы полевых транзисторов (на рис. 7.5 цепи управления не показаны). Такое изображение допустимо, так как транзисторы работают в ключевом режиме, а входное сопротивление полевого транзистора высокое. Заметим, что номера комбинаций на рис. 7.5 совпадают с номерами строк в таблице истинности. Рассмотренные примеры показывают, как аппаратно (схемотехнически) реализуются некоторые логические операции.

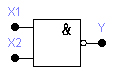

Рис. 7.6. Условное графическое обозначение элемента И-НЕ

Условное графическое обозначение элемента И-НЕ показано на рис. 7.6. Кружок на выходе логического элемента говорит о том, что элемент выполняет операцию инверсии (отрицание, НЕ). Символ & внутри прямоугольника свидетельствует о том, что данный элемент выполняет логическую операцию конъюнкции (логическое умножение, И). Два указанных символа совместно обозначают логическую операцию И-НЕ.

Элементы, реализующие другие логические функции, имеют иную конфигурацию (иную схему построения).

Заметим, что на базе логических элементов строятся все цифровые устройства: дешифраторы, сумматоры, триггеры, регистры и т.д.

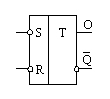

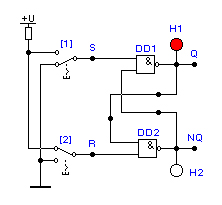

Рассмотрим принцип действия ещё одного важного элемента цифровых ЭВМ – триггера (рис. 7.7).

Рис. 7.7. Условное графическое обозначение RS-триггера

Существует несколько широко распространенных типов триггеров: RS-, D-, T-, JK- триггеры и др. Простейшими являются RS-триггеры, причем они входят в состав более сложных конструкций. Триггеры D-типа используются для построения регистров. T-триггеры являются счетными, они делят частоту входного сигнала на два и служат для построения двоичных счетчиков. JK-триггеры универсальны. На их основе можно реализовать любой из перечисленных типов триггеров.

Условное графическое обозначение RS-триггера показано на рис. 7.7. Буквы RS являются аббревиатурой английских слов Reset (сброс) и Set (установка). Триггер управляется сигналом логического нуля (активный сигнал 0). Если на S-вход подать сигнал логического нуля, а на R-вход – сигнал логической единицы, то триггер установится в единичное состояние. При этом на прямом выходе Q будет присутствовать сигнал логической единицы, а на инверсном выходе  – сигнал логического нуля. Если теперь на оба входа триггера подать сигналы логической единицы, то он перейдет в режим хранения информации. Его состояние не изменится до прихода новых управляющих сигналов, поступающих на входы R и S.

– сигнал логического нуля. Если теперь на оба входа триггера подать сигналы логической единицы, то он перейдет в режим хранения информации. Его состояние не изменится до прихода новых управляющих сигналов, поступающих на входы R и S.

Рис. 7.8. Принцип действия RS-триггера

Принцип действия RS-триггера удобно пояснить с помощью рис. 7.8., на котором изображен триггер, построенный на логических элементах И-НЕ.

С помощью переключателей 1 и 2 легко изменять сигналы на входах логических элементов DD1 и DD2. Показанное на рисунке состояние соответствует подаче логического нуля на элемент DD1 и логической единицы на элемент DD2. Заметим, что логическому нулю соответствует потенциал, близкий к нулю (поэтому переключатель 1 подсоединен к корпусу, земле устройства). Логической единице соответствует некоторое положительное напряжение. По этой причине вход R триггера через переключатель 2 и резистор подсоединен к источнику напряжения +U. В соответствии с таблицей истинности для логического элемента И-НЕ (табл. 7.2) на выходе Q элемента DD1 появится сигнал логической единицы (светодиод Н1 загорится). Сигнал логической единицы с выхода элемента DD1 подается на верхний вход элемента DD2, на нижний вход которого в это время также подается сигнал логической единицы.

В соответствии с таблицей истинности элемента И-НЕ (табл. 7.2) на выходе DD2 появится логический ноль (светодиод Н2 погаснет). Триггер установится в единичное состояние. Такая комбинация входных сигналов соответствует режиму установки триггера в единичное состояние.

Если теперь переключатель 1 переместить в верхнее положение (подать сигнал логической единицы на вход S), то триггер перейдет в режим хранения информации. Его состояние останется прежним, так как на нижний вход элемента DD1 подается сигнал логического нуля.

Чтобы изменить состояние триггера (перевести его в нулевое состояние), следует на вход R подать сигнал логического нуля. Для этого нужно переключатель 2 перевести в нижнее положение. Сигнал логического нуля на нижнем входе элемента DD2 вызовет появление логической единицы на инверсном выходе триггера NQ. В результате загорится светодиод Н2, а сигнал логической единицы с выхода DD2 попадет на нижний вход элемента DD1. В соответствии с таблицей истинности (табл. 7.2), наличие двух единиц на входах приведет к появлению логического нуля на выходе элемента И-НЕ. Триггер перейдет в нулевое состояние. Указанная комбинация входных сигналов соответствует режиму записи нуля.

Триггеры являются основными элементами, из которых состоит статическая оперативная память. На триггерах строят счетчики и регистры. С помощью регистров, например, осуществляется операция сдвига, которая нужна для реализации операции умножения. С помощью регистров преобразуют параллельный код в последовательный (и наоборот). Это необходимо, на-пример, для работы модема (многоразрядные слова, циркулирующие внутри ЭВМ, нужно передавать по двухпроводной линии связи).

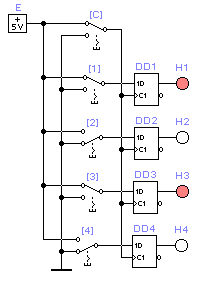

На рисунке 7.9. показан четырехразрядный регистр памяти, построенный на синхронных D-триггерах. Информация в триггеры DD1…DD4 записывается при поступлении на входы C1 разрешающего (синхронизирующего) импульса. Синхронизирующий сигнал формируется с помощью ключа С. В каждый триггер записывается та информация, которая присутствует на входе D. Например, на входе D триггера DD1 присутствует сигнал логической единицы, поэтому он установится в единичное состояние и светодиод Н1 загорится. В это же время триггер DD2 установится в нулевое состояние, так как на его D-входе присутствует логический ноль. Этот сигнал сформирован с помощью ключа 2.

Рис. 7.9. Четырехразрядный регистр памяти

| ← 7.2. Архитектура ЭВМ | 7.4. Контрольные вопросы и задания → |