Главная страница / 6. Логические основы ЭВМ: 6.1. Бистабильная ячейка ...

6.1. Бистабильная ячейка – триггер

| ← 6.Введение | 6.2. Регистры → |

Триггер — это электронная схема, широко применяемая в регистрах компьютера для надежного запоминания одного разряда двоичного кода. Триггер имеет два устойчивых состояния, одно из которых соответствует двоичной единице, а другое — двоичному нулю.

Термин триггер происходит от англ. trigger — защелка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flip-flop, что в переводе означает «хлопанье». Это звукоподражательное название электронной схемы указывает на ее способность почти мгновенно переходить («перебрасываться») из одного электрического состояния в другое и наоборот.

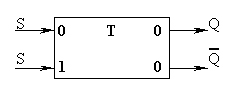

Самый распространенный тип триггера — так называемый RS-триггер (S и R, соответственно, от англ. set — установка, reset — сброс). Условное обозначение триггера дано на рис. 6.1.

Рис. 6.1. Условное обозначение триггера

Он имеет два симметричных входа S и R и два симметричных выхода Q и  , причем выходной сигнал Q является логическим отрицанием сигнала

, причем выходной сигнал Q является логическим отрицанием сигнала  .

.

На каждый из двух входов S и R могут подаваться входные сигналы в виде кратковременных импульсов ( ).

).

Наличие импульса на входе будем считать единицей, а его отсутствие — нулем.

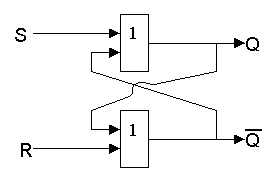

На рис. 6.2 показана реализация триггера с помощью вентилей ИЛИ-НЕ, соответствующая таблица истинности приведена в табл. 6.1.

Рис. 6.2. Реализация триггера с помощью вентилей ИЛИ-НЕ

Таблица 6.1. Таблица истинности триггера

| S | R | Q |  |

|---|---|---|---|

| 0 | 0 | Запрещено | |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | Хранение бита | |

Проанализируем возможные комбинации значений входов R и S триггера, используя его схему и таблицу истинности схемы ИЛИ-НЕ (табл. 6.1).

- Если на входы триггера подать S=1, R=0, то (независимо от состояния) на выходе Q верхнего вентиля появится 0. После этого на входах нижнего вентиля окажется R=0, Q=0 и выход

станет равным 1.

станет равным 1. - Точно так же при подаче 0 на вход S и 1 на вход R на выходе

появится 0, а на Q — 1.

появится 0, а на Q — 1. - Если на входы R и S подана логическая 1, то состояние Q и

не меняется.

не меняется. - Подача на оба входа R и S логического 0 может привести к неоднозначному результату, поэтому эта комбинация входных сигналов запрещена.

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания 1 байта нужно 8 триггеров, для запоминания 1 Кбайта — соответственно 8 · 210 = 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

| ← 6.Введение | 6.2. Регистры → |